Among the artists using AI to enhance and accelerate their creative endeavors is Sabour Amirazodi, a creator and tech marketing and workflow specialist at NVIDIA.

A new cell-phone-sized device—which can be deployed in vast, remote areas—is using AI to identify and geolocate wildlife to help conservationists track…

A new cell-phone-sized device—which can be deployed in vast, remote areas—is using AI to identify and geolocate wildlife to help conservationists track…

A new cell-phone-sized device—which can be deployed in vast, remote areas—is using AI to identify and geolocate wildlife to help conservationists track endangered species, including wolves around Yellowstone National Park. The battery-powered devices—dubbed GrizCams—are designed by a small Montana startup, Grizzly Systems. Together with biologists, they’re deploying a constellation of the…

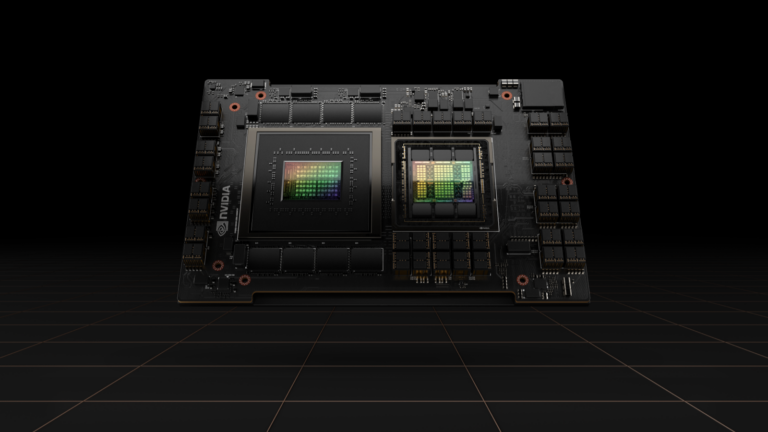

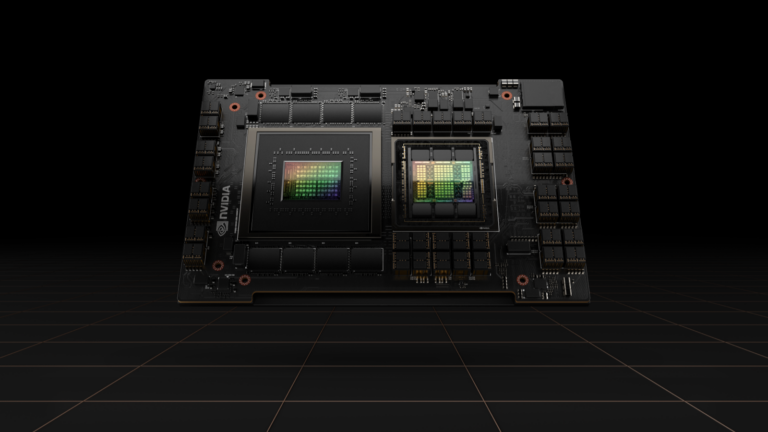

As the world transitions from general-purpose to accelerated computing, finding a path to building data center infrastructure at scale is becoming more important than ever. Enterprises must navigate uncharted waters when designing and deploying infrastructure to support these new AI workloads. Constant developments in model capabilities and software frameworks, along with the novelty of these

Read Article

As the world transitions from general-purpose to accelerated computing, finding a path to building data center infrastructure at scale is becoming more important than ever. Enterprises must navigate uncharted waters when designing and deploying infrastructure to support these new AI workloads. Constant developments in model capabilities and software frameworks, along with the novelty of these

Read Article

AI agents are emerging as the newest way for organizations to increase efficiency, improve productivity, and accelerate innovation. These agents are more…

AI agents are emerging as the newest way for organizations to increase efficiency, improve productivity, and accelerate innovation. These agents are more…

AI agents are emerging as the newest way for organizations to increase efficiency, improve productivity, and accelerate innovation. These agents are more advanced than prior AI applications, with the ability to autonomously reason through tasks, call out to other tools, and incorporate both enterprise data and employee knowledge to produce valuable business outcomes. They’re being embedded into…

AI agents are emerging as the newest way for organizations to increase efficiency, improve productivity, and accelerate innovation. These agents are more…

AI agents are emerging as the newest way for organizations to increase efficiency, improve productivity, and accelerate innovation. These agents are more…

AI agents are emerging as the newest way for organizations to increase efficiency, improve productivity, and accelerate innovation. These agents are more advanced than prior AI applications, with the ability to autonomously reason through tasks, call out to other tools, and incorporate both enterprise data and employee knowledge to produce valuable business outcomes. They’re being embedded into…

An Introduction to Model Merging for LLMs

![]() One challenge organizations face when customizing large language models (LLMs) is the need to run multiple experiments, which produces only one useful model….

One challenge organizations face when customizing large language models (LLMs) is the need to run multiple experiments, which produces only one useful model….![]()

One challenge organizations face when customizing large language models (LLMs) is the need to run multiple experiments, which produces only one useful model. While the cost of experimentation is typically low, and the results well worth the effort, this experimentation process does involve “wasted” resources, such as compute assets spent without their product being utilized…

Learn how to build scalable data processing pipelines to create high-quality datasets.

Learn how to build scalable data processing pipelines to create high-quality datasets.

Learn how to build scalable data processing pipelines to create high-quality datasets.

Deploying large language models (LLMs) in production environments often requires making hard trade-offs between enhancing user interactivity and increasing…

Deploying large language models (LLMs) in production environments often requires making hard trade-offs between enhancing user interactivity and increasing…

Deploying large language models (LLMs) in production environments often requires making hard trade-offs between enhancing user interactivity and increasing system throughput. While enhancing user interactivity requires minimizing time to first token (TTFT), increasing throughput requires increasing tokens per second. Improving one aspect often results in the decline of the other…